Service hotline

+86 0755-83044319

release time:2022-03-17Author source:SlkorBrowse:11873

保守来讲,当下8英寸(200mm)晶圆的供应链情况相当严峻!

然而,这绝不是新问题。中国台湾的市场调查公司一一TrendForce于2020年11月发布新闻称:“就8英寸晶圆的产能而言,自2019年下半年以来一直持续在严重的供给不足问题”。

此外,雪上加霜的是2021年3月瑞萨电子那珂工厂发生了火灾。由于瑞萨的此处工厂为诸多车型供货,因此导致问题更加恶化。

基于以上背景,导致诸多因素“纠缠”在一起。但是,不言而喻,[敏感词]的原因还是在于新冠疫情(COVID-19)。由于新冠疫情的发生,耳机、电脑、电视、显示屏、手机等各种电子产品的需求猛增。

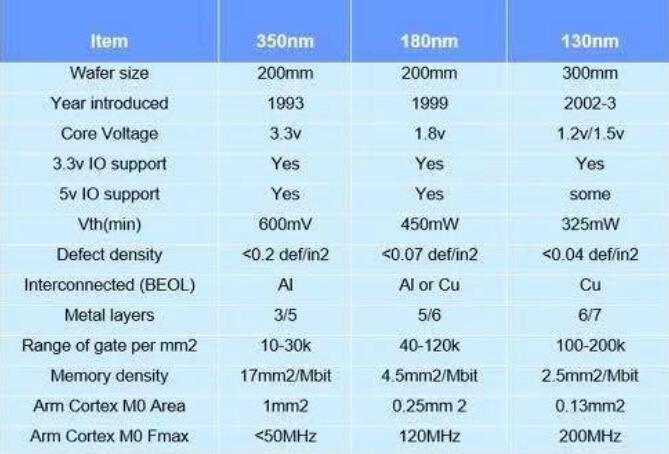

虽然汽车也属于以上范畴,但人们还是希望汽车市场会在2021年内从新冠疫情的阴影中恢复。如今各种产品都在推广将多种功能汇集于一体的SoC(System on Chip)模式,因此很多产品都需要搭载多个具备数模混合信号(Mixed Signal Chip)的IC。以上产品的用途方向主要有以下:PMIC(Power Management IC)、CMOS图像传感器、指纹识别传感器、汽车发动机/底盘控制、显示屏驱动IC、Sub Giga Hertz的无线通信芯片等。一般情况下,以上这些都适用180纳米、350纳米工艺,用8英寸晶圆生产。

即,用于这种数模混合信号芯片(Mixed Signal Chip)、功率半导体的产品需求不断增长,这导致了8英寸晶圆的产能不足。

受到8英寸晶圆的供给达到极限的影响,代工厂(Foundry)很有可能会扩大产能。代工厂可能会收购垂直统筹型厂家(IDM:Integrated Device Manufacturer)的8英寸晶圆生产设备和产线。可列举的事例如下:最近有报道指出,中国台湾的UMC正在讨论收购Japan Semiconductor(原东芝的半导体制造公司) 的8英寸产线。

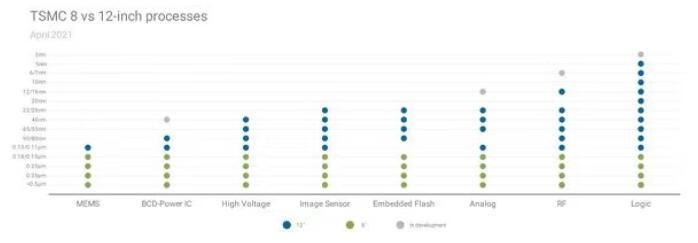

用于Mixed Signal ASIC等产品的主要节点技术比较图。(图片出自:eetimes)

12英寸晶圆技术有多个优势。由于可代替旧代际技术中的铝而使用铜,因此电流密度允许值也较高,耐电迁移性也较[敏感词]。此外,金属层的层数也较多,晶体管尺寸较小,因此,通过提高晶体管密度、布线密度,可以缩小芯片尺寸、提高性能。此次的半导体供给不足问题某种程度上是一个“警告”,如今使用8英寸晶圆的企业应该首先考虑一下未来的需求。此外,无论是主要生产据点,还是第二供应商(Second Source),在所有的工艺完成之前都需要确保足够的时间。

免责声明:本文转载自“半导体行业观察”,本文仅代表作者个人观点,不代表萨科微及行业观点,只为转载与分享,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。

公司电话:+86-0755-83044319

传真/FAX:+86-0755-83975897

邮箱:1615456225@qq.com

QQ:3518641314 李经理

QQ:332496225 丘经理

地址:深圳市龙华新区民治大道1079号展滔科技大厦C座809室

Site Map | 萨科微 | 金航标 | Slkor | Kinghelm

RU | FR | DE | IT | ES | PT | JA | KO | AR | TR | TH | MS | VI | MG | FA | ZH-TW | HR | BG | SD| GD | SN | SM | PS | LB | KY | KU | HAW | CO | AM | UZ | TG | SU | ST | ML | KK | NY | ZU | YO | TE | TA | SO| PA| NE | MN | MI | LA | LO | KM | KN

| JW | IG | HMN | HA | EO | CEB | BS | BN | UR | HT | KA | EU | AZ | HY | YI |MK | IS | BE | CY | GA | SW | SV | AF | FA | TR | TH | MT | HU | GL | ET | NL | DA | CS | FI | EL | HI | NO | PL | RO | CA | TL | IW | LV | ID | LT | SR | SQ | SL | UK

Copyright ©2015-2025 Shenzhen Slkor Micro Semicon Co., Ltd