Service hotline

+86 0755-83044319

release time:2022-03-16Author source:SlkorBrowse:12595

摘要:

为满足对更高数据吞吐量的需求,半导体公司正在开发更快的无线、有线和光学接口。其主要是基于BiCMOS,高级CMOS工艺和FinFET节点在ESD敏感电路的实现。然而,传统ESD解决方案的寄生电容限制了信号频率。本文介绍了用于高速SerDes(28Gbps至112Gbps)电路的台积电([敏感词])28nm CMOS和台积电([敏感词]) 16nm,12nm,7nm FinFET工艺中使用的小面积,低电容模拟I/O。ESD解决方案的寄生电容降低到100fF以下,而某些硅光子学中的应用甚至降低到20fF以下。

I.简介

当今世界,数据传输的需求与日俱增。人们日常观看视频所消耗的数据流量不断增加。随着智能手机的普及,电脑的应用,数据中心和长距离信息交流等不断发展,各种带宽需求不断增长。这一需求又推动了半导体行业不断发展,进而寻求更快的无线、有线和光学接口的研发。几年前,速度限制约为10 Gbps。而近来,电路却以56Gbps甚至112Gbps的速度在运行。

对于这样的高速通信接口,芯片设计人员需要限制连接到接口的芯片上ESD保护钳位的寄生电容。由于传统的ESD方法还存在不足,因此需要特制的模拟I/O电路。本文演示了经过硅验证的ESD解决方案,适用于CMOS工艺中[敏感词] 28nm和FinFET工艺中[敏感词] 16nm,12nm和7nm。ESD解决方案的寄生电容降低到100fF以下,而某些硅光子应用,甚至降低到20fF以下。

II.传统的ESD方法

图1显示了模拟I/O PAD模块的传统ESD方法。它由一个连接Vss到I/O PAD的二极管和连接I/O PAD模块到Vdd的二极管以及在Vdd和Vss之间的电源/轨钳位组成[1-5]。

IC设计人员之所以喜欢它,是因为这两个二极管的设计容易实现且硅占用面积小,寄生电容相当低。

图1:应用于许多I/O PAD模块的传统ESD方法:一个从Vss到I/O的二极管,另一个从I/O到Vdd的二极管。一个动力钳用于1/2应力组合。

对于敏感节点,IC设计人员会在I/O与电路之间增加一个隔离电阻,以增加ESD设计窗口。如果功能电路无法处理静电释放(ESD)电流,则在隔离电阻后面添加一个次级钳位(图2)。

图2:有时,IC设计人员会在I/O PAD模块和电路之间增加一个电阻,并在敏感电路前安放一个小的次级钳位。这会增加ESD设计窗口。

这种简单的方法存在多个问题,特别是高速接口的问题:

(1)隔离电阻严重影响高速运行效果并增加了噪声。

(2)ESD二极管可能会在信号PAD和电源线之间引入过多的寄生电容。

(3)由于PAD和Vdd之间的噪声耦合或信号电压可能高于参考Vdd电压,也有可能是因为配型问题,某些接口无法承受从I/O PAD模块到Vdd的二极管带来的电压刺激。

(4)对于敏感节点,预期ESD电流路径上的总压降可能高于功能电路的故障电压[5]。

减少电容(问题2)并提高电压容限(问题3)的简单方法是串联使用2个或更多个二极管。但是,这会导致在ESD应力出现更高的电压降,从而恶化问题4。2017年,提出了具有新型双极概念的替代方案[6-7]。

本文讨论的项目中,IC设计人员使用局部保护钳位概念代替了传统的双二极管ESD方法,如图3所示。如果功能性操作不能承受二极管从“ IN”到Vdd,则可以将其取下。这对于安全故障,热插拔,漏极开路输出,冷备用输入或耐压过高的接口来说是很典型的现象[8]。

图3:采用局部钳位ESD保护的简化电路原理图。如果需要进行功能操作,则可以去除IN和Vdd之间的二极管。在某些情况下,Vdd和“ IN”之间会再添加一个钳位。

局部钳位方法具有很多优点:

(1)减少对总线电阻的依赖

(2)ESD条件下的压降大大降低,而无需隔离电阻,非常适合敏感节点。

(3)为减少寄生电容提供了不同的选项(请参见[敏感词]的案例研究)

(4)可以分别针对每个I/O PAD进行优化。例如: 一些PAD可能需要更高的ESD耐受性,否则无法承受I/O和Vdd之间二极管的放电。

III.SerDes保护案例研究

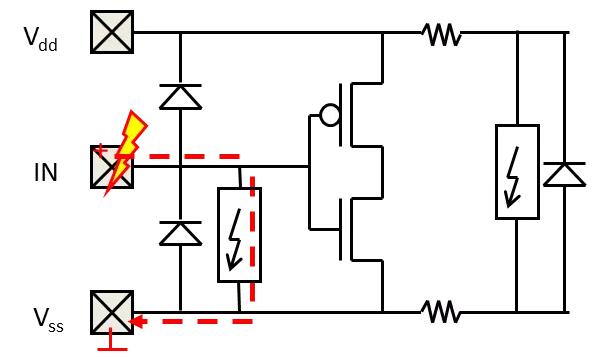

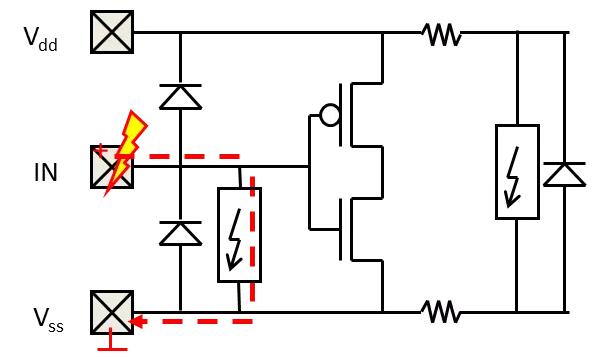

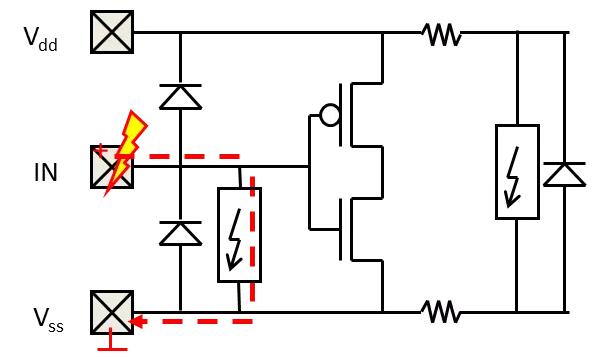

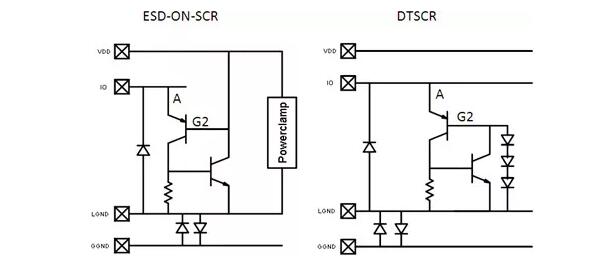

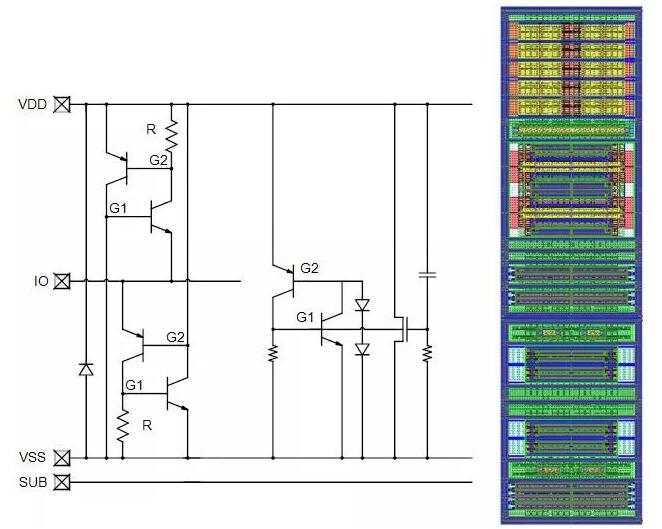

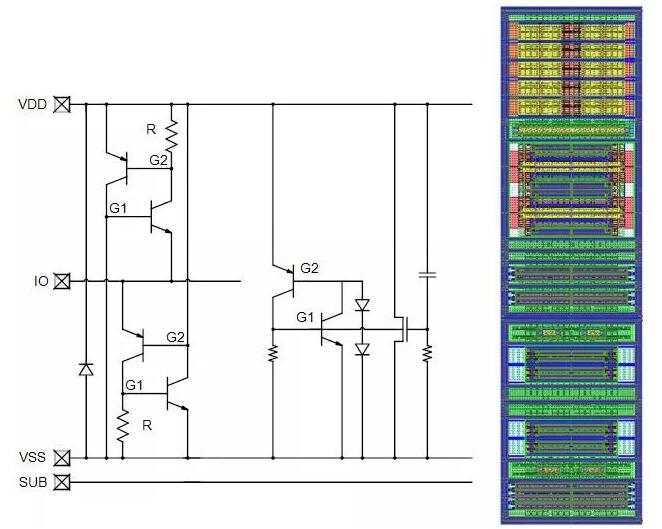

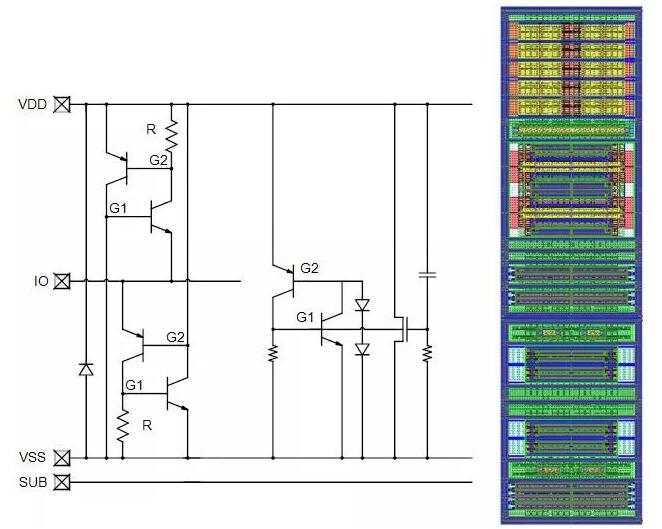

[敏感词]的案例研究总结了几种具有(超)低寄生电容的局部钳位方法,以保护从28nm CMOS到7nm FinFET各类的高速SerDes接口。在案例研究中使用了基于SCR的不同类型的局部钳位(图4)。二极管触发式SCR和ESD-on-SCR以前用于保护无线LNA接口[9]。

图4:案例研究中使用的两个ESD保护夹。一旦IO电平将二极管压降(Anode-G2)升高到高于Vdd电压,就会触发Sofics ESD-on-SCR。一旦AnodeG2和触发二极管被正向偏置,则Sofics DTSCR打开。

1.FPGA 28nm, 28Gbps SerDes

台积电([敏感词])28nm中的一系列高级FPGA产品,客户需要定制的ESD保护单元。28Gbps SerDes接口需要以下规格:

-寄生电容远低于100fF。

-ESD等级:> 1kV HBM;> 250V CDM

选择了Sofics DTSCR钳位的缩小版本作为Tx和Rx接口的本地保护。在隔离电阻后面增加了一个次级本地CDM钳位,以保护Rx情况下的薄栅极氧化物(图5)。DTSCR,反向二极管和金属连接的寄生电容保持在80fF以下。

图5:28Gbps SerDes Rx(输入)阶段的示意图,显示了用于增强CDM保护的DTSCR本地钳位和二级保护阶段。

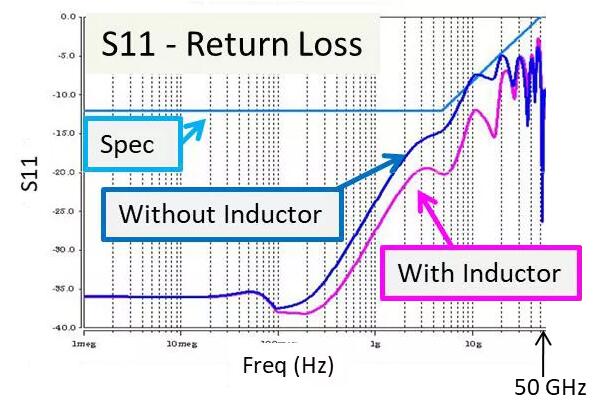

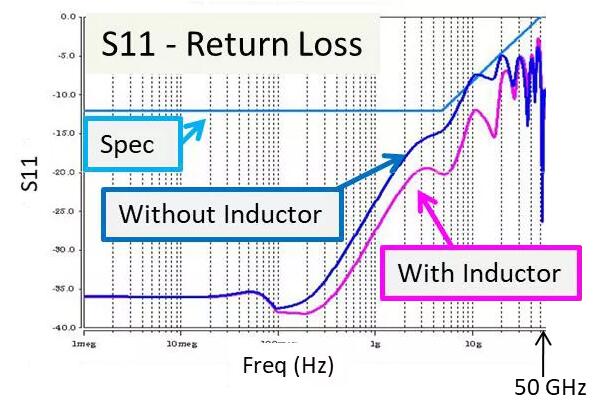

为了满足S11–回波损耗规范,在DTSCR上串联了一个电感器(图6)。符合包括CDM在内的所有规范。FPGA器件以4.5A的峰值电流达到300V以上。所有分析结果均已在IEW 2011活动中展示[10]。

图6:为了满足S11规范,在DTSCR上串联了一个电感器。线圈降低了10 GHz和20 GHz时的S11峰值。

2.通用SerDes 16nm,28Gbps

具有16纳米制程的28 Gbps SerDes的高速(数据中心)通信芯片需要定制的ESD保护方案。

本地ESD钳位必须满足这些要求:

-在ESD应力低于3.3V时具有故障电压的敏感薄氧化物0.8V核心晶体管的保护

-低泄漏ESD钳位,在高温(125°C)下低于10nA

-小硅片占用空间,可在同一通信芯片上启用多个通道

-无电阻

- > 2kV HBM

-[敏感词]ESD结电容为100fF

图7:Tx接口的差分对的保护概念的示意图。在差分对的两个路径上都添加了一个本地钳位和并联反向二极管。

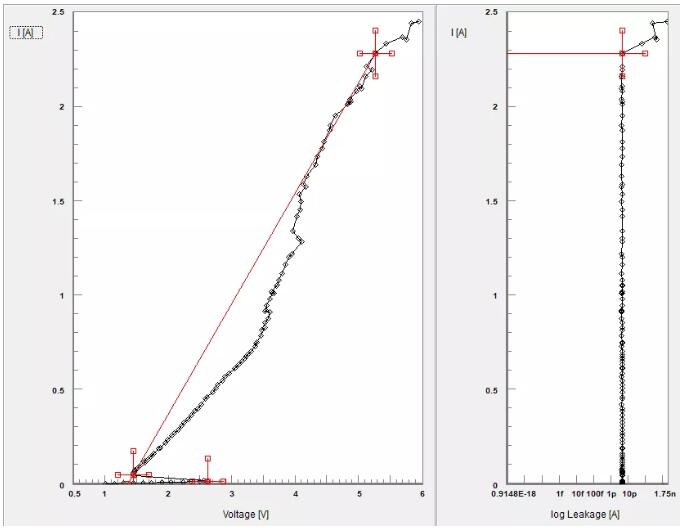

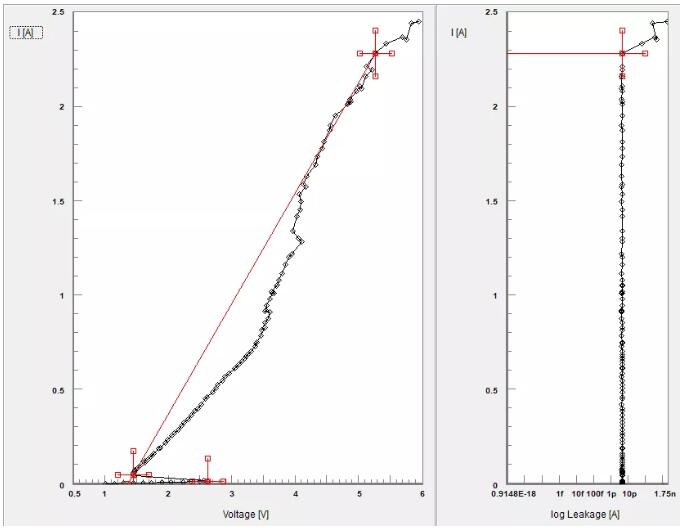

基于对[敏感词]16nm FinFET技术的芯片进行的广泛分析,选择了ESD-on-SCR概念作为本地钳位器件。TLP数据如图8所示。

在小于1.000um²的面积内保护2安培以上的薄氧化物器件。高温下的泄漏约为1nA。

图8:用作本地钳位器件的SCR上ESD器件的TLP测量。在达到薄氧化物晶体管的故障电压之前,器件达到2A以上。

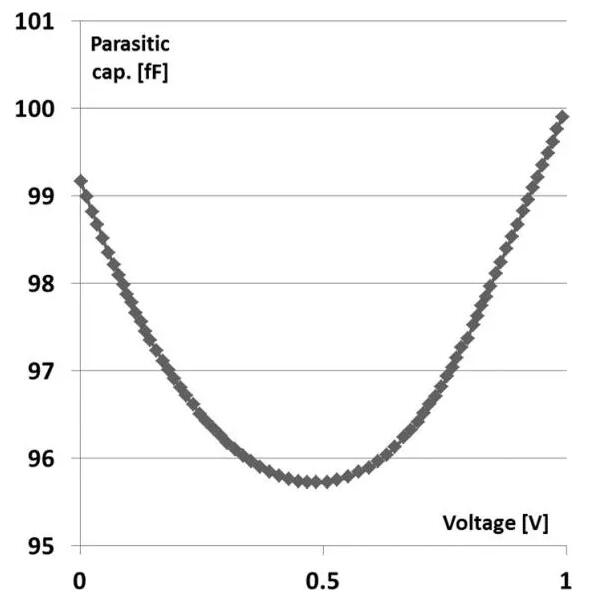

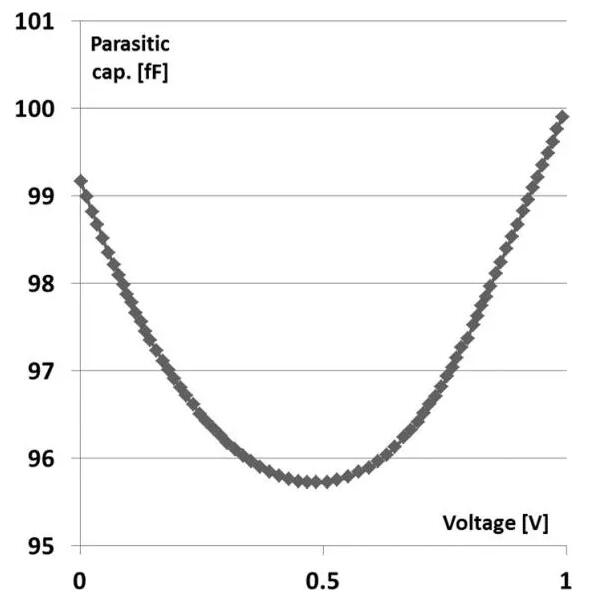

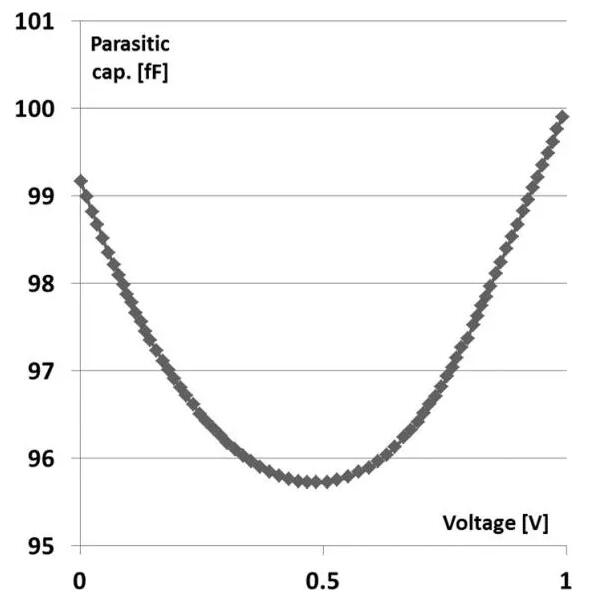

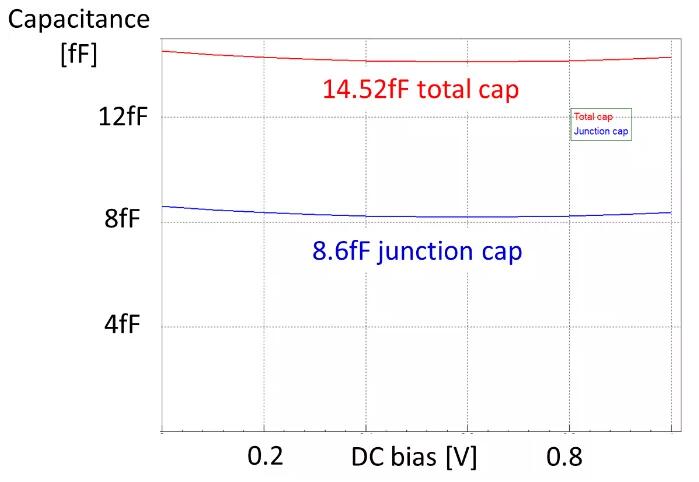

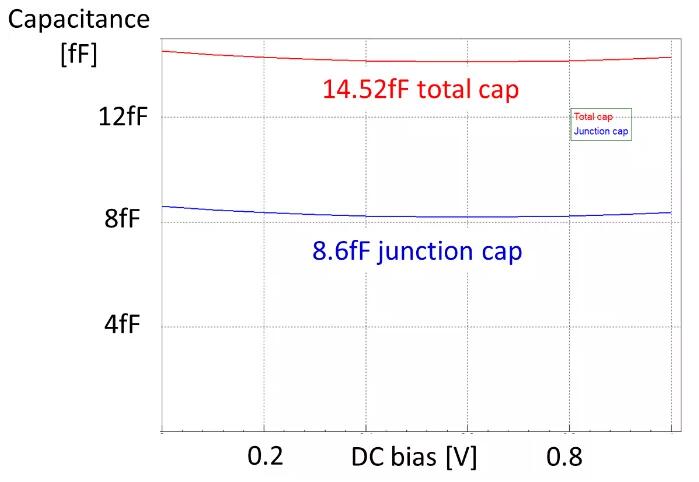

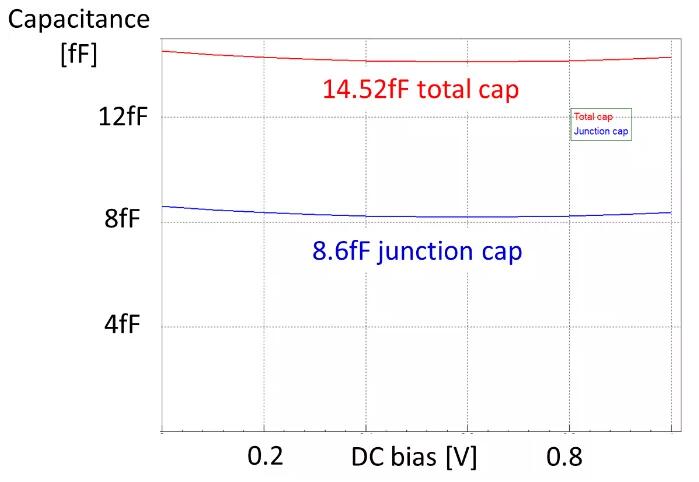

图9:SCR上ESD的电容仿真(Spice)。在PAD的电压范围内,电容均保持在100fF的目标电平以下。

为了确保ESD保护钳位不影响高速SerDes的运行,在PAD电压上模拟了寄生结电容,如图9所示。使用了基于二极管结的等效模型来模拟静电保护单元的电容负载。

3.硅光子学28nm,28Gbps

几家从事新型光收发器工作的公司联系我们寻求支持。对于常规的低速I/O(1.8V),铸造厂提供的模拟/数字I/O库已足够。这些PAD的ESD要求为2kV HBM。

另一方面,代工厂库中的模拟I/O为高速接口引入了过多的寄生电容。设计人员要求将ESD的总电容减小到15fF以下。

28nm CMOS SoC与硅光子器件共同封装在共享/混合集成封装中(图10)。由于这种倒装芯片组装是在ESD控制的环境中进行的,因此ESD保护级别可以降低至200V HBM,而不会影响成品率。

图10 :(示例)使用倒装芯片键合工艺将电子IC(驱动器)封装在硅光子器件上(©IOP 2016 [11])。

图11:在硅光子SerDes接口中使用的简化的Tx /输出电路。

28Gbps接口使用差分对概念,如图11所示。使用0.9V核心晶体管创建1V功能电路,以确保可以达到开关速度。但是,这些晶体管将Rx,Tx信号的可用ESD设计窗口减小到4V。

ESD保护的其他要求包括低漏电操作和小硅面积。

ESD保护设计包括完整的本地保护钳位概念,如图12所示。集成了1V电源钳位,以确保所有应力情况都可以在接口处进行本地处理,并消除了母线电阻的影响。整个钳位结构与基板隔离,以减少来自衬底的噪声,这些噪声可能来自芯片上与之较远的数字电路。

图12:SerDes电路的Rx和Tx节点的完整本地保护方法的示意图(左)。基于SCR上的ESD器件。基于SCR的1V电源钳夹集成在同一布局中(右)。ESD的总面积为683.75um²。

I/O PAD模块上的总寄生电容包括不同方面。结电容可以很容易地从代工厂提供的二极管Spice模型中得出。本地ESD钳位的金属连接会增加大量电容。寄生金属电容可以从PEX提取中得出。减小金属连接的宽度可以减小电容,但也会降低线路的稳定性。最小金属宽度是由我们通过对不同弄金属实施ESD应力得出的。

当客户要求使用超低电容(远低于100fF)的ESD保护时,PEX提取中将包括Metal dummy部分。

通过迭代过程(布局,PEX提取),ESD钳位电路的总寄生电容减小至小于15fF。下图将显示此过程中的不同步骤。下图(图13)显示了电容值与PAD上偏置电压的关系。

必须减小对地的寄生电容,以防止高频信号分流到地。

公式1:电容电抗Xc(以欧姆为单位)与信号频率(f)和电容(C)成反比

对于高频(> 50 Ghz),寄生电容表现为对地的电阻。该阻抗必须足够高。15 fF的电容在50 GHz时的电阻约为200欧姆。

在迭代过程中,为了减少金属连接对寄生电容的影响,使用了一些规则

-移除不必要的过孔连接

-尽可能减少金属1,仅将其放在连接扩散区的顶部。

-防止金属层1穿过结区。

-垂直(向上)连接

即使通过以上方法降低寄生电容,在高级节点上仍有42%的寄生电容与金属连接有关。

图13:I / O电压上的寄生电容(仅总电容和结电容)。

使用HBM ESD应力的瞬态Spice模拟,将图12的局部钳位方法与其他2个概念进行了比较

-概念1:建议的局部钳位

-概念2:Foundry提供的I/O PAD模块(双二极管和Foundry建议的核心功率钳位)

-概念3:双二极管与Sofics 1V核心保护钳位组合

从图14可以清楚地看到,概念2和3产生的压降远高于基于薄氧化物晶体管[12]的敏感电路的故障电压(4V)[12]。

图14:HBM应力下的瞬态Spice模拟。比较了3个概念,以验证在ESD应力期间敏感节点上的电压降保持在[敏感词]4V以下。只有建议的局部钳位才能使ESD应力低于4V。使用1kV HBM应力和ESD器件缩放至1kV稳健性进行了比较。使用组合的NPN/PNP模型模拟SCR局部钳位的骤回。

4.硅光子7nm FinFET

为了进一步增加光互连的带宽(超过56 Gbps),我们的客户采用了[敏感词] 7nm FinFET技术。

所提出的解决方案类似于图12。创建了两种版本的ESD保护,一种具有50fF的寄生电容,另一种具有15fF以下的小电容。在论文中,将包括这些案例研究。

台积电([敏感词])的7纳米FinFET工艺的初步测试表明,SCR上的ESD本地钳位电路具有预期的效果(图15)。

在7nm技术中,内核晶体管(栅极到源极和漏极到源极)的故障电压约为3V。幸运的是,在许多SerDes应用中,由于其他晶体管串联在一起,会有更多的余量(图11)。根据电路原理,这些电路的故障电压约为4-5V。

7nm ESD钳位已集成到2个用于高速接口的设计中。在撰写本文时,这些产品样本尚未到位,因此CDM数据尚不可用。

图15:基于[敏感词] 7nm技术的ESD-on-SCR概念的TLP分析。保护敏感的内核晶体管。这种用于2kV HBM性能的参考器件已按比例缩小到15fF和50fF版本,以保护高速SerDes。

总结

用于模拟I/O PAD模块的传统“双二极管” ESD保护概念在保护高级CMOS和FinFET节点中的高速SerDes接口时遇到了问题。二极管,总线电阻和功率钳位上的总压降很容易超过核心晶体管的故障电压。此外,“二极管向上”增加了限制因素。

这项工作显示了几个案例研究,其中双二极管概念被替换为本地ESD保护钳位。

基于专有的二极管触发和ESD-on-SCR器件的I/O PAD模块。本地钳位降低了总线电阻的依赖性,降低了钳位电压,并允许分别优化每个模拟I/O。此外,这些案例表明,可以创建具有非常低的寄生电容和较小的硅面积的ESD保护。

数据基于高级CMOS和FinFET节点上的专用ESD测试芯片。这项工作中的模拟I/O被20多家公司用于保护28nm CMOS,16nm/12nm和7nm FinFET技术的高速SerDes接口。

免责声明:本文转载自“IP与SOC设计”,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。

Site Map | 萨科微 | 金航标 | Slkor | Kinghelm

RU | FR | DE | IT | ES | PT | JA | KO | AR | TR | TH | MS | VI | MG | FA | ZH-TW | HR | BG | SD| GD | SN | SM | PS | LB | KY | KU | HAW | CO | AM | UZ | TG | SU | ST | ML | KK | NY | ZU | YO | TE | TA | SO| PA| NE | MN | MI | LA | LO | KM | KN

| JW | IG | HMN | HA | EO | CEB | BS | BN | UR | HT | KA | EU | AZ | HY | YI |MK | IS | BE | CY | GA | SW | SV | AF | FA | TR | TH | MT | HU | GL | ET | NL | DA | CS | FI | EL | HI | NO | PL | RO | CA | TL | IW | LV | ID | LT | SR | SQ | SL | UK

Copyright ©2015-2025 Shenzhen Slkor Micro Semicon Co., Ltd