【新智元导读】传统集成电路设计费时又费力,能否用人工智能来提高工作效率?在今年的集成固态电路会议上,包括Google AI负责人Jeff Dean在内的四位大佬阐述了AI的应用对处理器、量子计算、结构创新等的重大影响。「新智元急聘主笔、编辑、运营经理、客户经理,添加HR微信(Dr-wly)或扫描文末二维码了解详情。」

今年的集成固态电路会议(ISSCC)的主题是“

为AI时代提供动力的集成电路”,而开幕全体会议的目的是描绘AI“折叠”半导体空间的程度。

Google AI 负责人Jeff Dean、联发科高级副总裁Kou-Hung Loh、Imec项目总监Nadine Collaert、IBM Research总监Dario Gil分别解释了电子领域对AI的期望要求,例如,如何驱动专门为AI应用而设计的新型处理器(以及CPU和GPU);促进结构创新(例如小芯片,多芯片封装,中介层);甚至影响着量子计算的发展。

布局布线太费时?Google AI 帮你降本增效

ISSCC会议于上周在旧金山举行,会议期间谷歌表示人工智能对电路设计同样重要,并且宣布

谷歌正在尝试利用机器学习来解决集成电路设计流程中自动化布局布线问题,并且得到了不错的效果。

人工智能的应用这几年来也一直是电子领域的研究热点和重点。这个方向吸引了大量半导体研究人员从事传统方向和人工智能结合的相关研究。尤其是今年的集成固态电路会议(ISSCC)甚至把会议主题定为:“

用集成电路推动AI新时代”。而开幕式也将此次会议的目的陈述为探讨AI对半导体领域研究的影响。

开幕式的四位发言人解释了人工智能的需求是如何推动设计AI专用的新型处理器(相比于CPU和GPU)、如何促进结构创新(例如采用小芯片,多芯片封装,或者插件式设计)、甚至如何正在影响未来量子 计算的发展。

会议的[敏感词]位发言人是Google AI负责人Jeff Dean。Jeff Dean提到谷歌正在通过实验,尝试

利用机器学习执行集成电路设计中的布局布线任务,也就是让AI学习集成电路中的布局布线,节省设计专家的人力劳动。

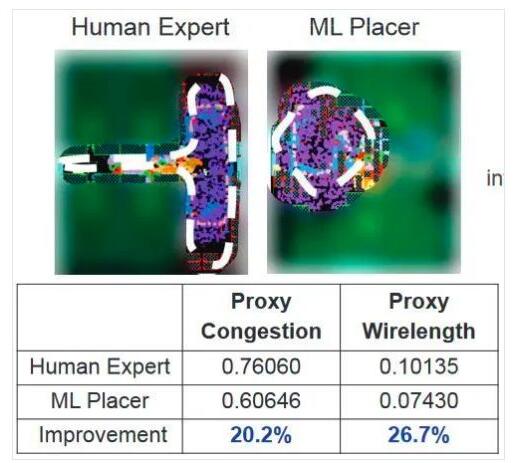

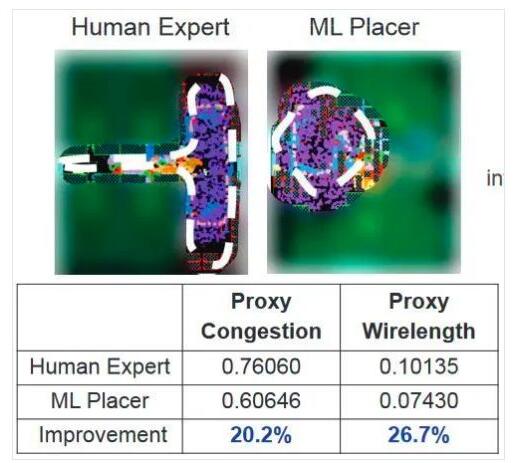

人类ASIC专家的布局布线结果和一个低功耗ML加速器芯片的布局布线结果对比。谷歌故意遮盖了部分图像。(来源:Google Research / ISSCC)

Jeff Dean首先简要介绍了AI和ML的发展历史,接着介绍了机器如何学习玩双陆棋,深蓝如何下国际象棋, alphago如何擅长下围棋 。以及现在的AI可以应对非常复杂的视频游戏(例如《星际争霸》)并且取得了“具有里程碑意义的成绩”。同时 机器学习还被广泛应用于医学成像,

机器人技术,计算机视觉,自动驾驶,神经科学,农业,天气预报等领域。

数十年来,推动计算技术发展的基本思想是:问题越大,我们就给它更强的计算能力。如果你拥有的处理能力越强,你就可以解决的更大的问题。在一段时间里,这个规则也适用于解决AI问题。但是,这个规则很快就被爆炸式增长的问题空间所打破。因为我们根本无法攒够足够多的CPU/GPU来解决这样的问题。

事实证明,

AI / ML不需要典型的CPU / GPU的复杂功能,所需的数学运算也更简单,而且要求的精度也低很多。这个发现带来的影响是:专用的AI / ML加速器不必像CPU / GPU那样复杂。基于此Google设计了TensorFlow加速器,并且已经推出第三代产品,第四代产品也很快会发布。AI / ML处理器设计相对简单,因此也相对便宜,所有这些都使得将机器学习进一步推向网络边缘变得更加容易。截至2019年,Google已经拥有一款可在智能手机上使用的非常紧凑的模型。

当前阶段每个基于AI的应用程序(自动驾驶,医学成像,游戏)都是通过训练专用的AI / ML系统而实现。那么,AI能将一个系统上学到的知识应用到从未见过的新系统中吗?答案很明确:“YES”。

“我之所以提出这一点是因为我们开始考虑将AI用于ASIC设计中的布局布线” Jeff Dean说,“

布局布线的难度远远大于围棋:目标更模糊,问题规模反而更大”。Google已经创建了布局布线的学习模型,然后尝试该工具是否可以进一步推广。Jeff Dean说“到目前为止,我们在所有尝试中都获得了非常好的结果。它的性能要比人类好一些,有时甚至要好很多。”

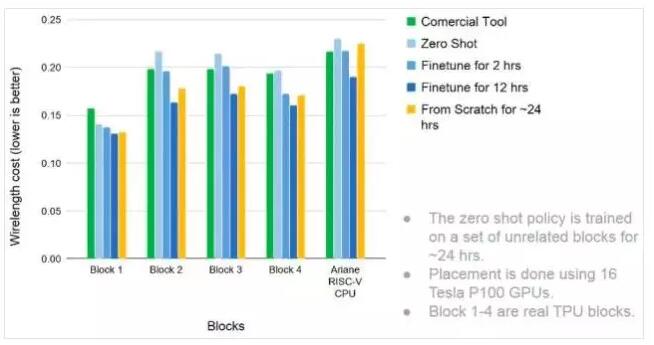

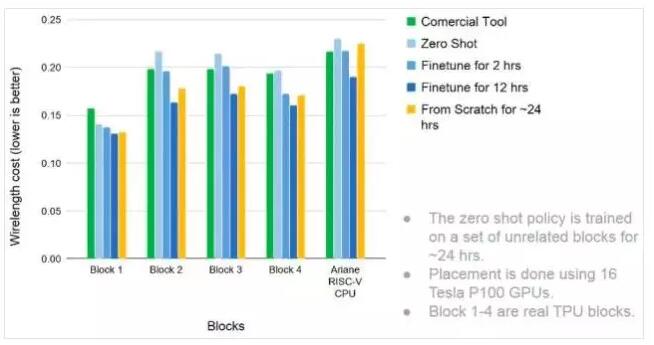

Google将使用机器学习布局和布线的效果与商用软件进行了比较。 测试电路是几个不同的模块,包括Ariane RISC-V CPU。(来源:Google Research / ISSCC)

“更好”指的是在非常短的时间内完成布局布线。如果让人类设计专家完成这项任务通常需要一周甚至数周时间。而

ML布局布线器通常在24小时内就能完成相同的工作量,并且布局的连线通常更短。ML布局布线器在自动布局和布线方面的更多出色表现可以参考由Cadence公司Rod Metcalfe撰写的“在EDA中进行机器学习可加快设计周期”的文章。

Jeff Dean说,ML可能还会扩展到IC设计过程的其他部分,包括使用ML来帮助生成测试用例,以更充分地进行ASIC设计验证;也许还可以使用ML来改进高级代码综合以达到更优化的设计。这些可能的应用方向对机器学习本身的普及很重要,同时对加速集成电路设计进度也是一样的重要。

高成本大功耗CPU/GPU并非必须,边缘计算可定制

联发科技高级副总裁兼首席战略官Kou-Hung Loh指出物联网设备将数百亿的事物连接在一起,然而AI正在改变着这些联网的一切事物。

AI之所以走向边缘计算,部分原因正如Dean在本节前面提到的那样,还有更多的原因包括:

减轻数据中心日益增长的处理负担、最小化网络流量,以及那些需要使用近似本地处理的实时应用。本地处理要求:快速(必须为AI计算专门设计),而且低功耗。这些为AI专门设计的处理器,被称为AI处理器单元。一个APU可以不如CPU灵活,但是由于是专用的,所以

APU可以性能上比CPU快20倍,功耗比CPU低55倍。

多系统不好协同设计?AI 帮你打通奇经八脉

Imec的项目总监Nadine Collaert指出摩尔定律可能在未来几年内依然适用,虽然CMOS缩小的难度越来越大,但可以利用FinFETs、 纳米片、forksheets等技术实现芯片级的CMOS进一步缩放。相信3D技术是[敏感词]的方法:包括使用多层封装,硅上穿孔,以及与其他标准单元进行精细等级的连接。具体技术的选择需要根据系统设计需求和可选用的器件属性来决定。“这将是一个复杂的练习”Collaert说。这将对EDA供应商产生很大压力,因为这需要EDA供应商在工具层面支持不同方案的尝试和比较。

无线通信系统的前端模块将成为一个特殊的挑战。“通常,这些系统最多样化:使用不同技术的许多不同组件,并且前端模块会随着天线、PA、以及滤波器的增多,而变得更加复杂。”

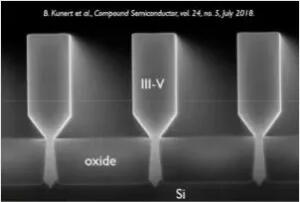

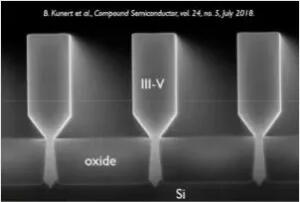

无线通信行业正在向更高频和更高效率迈进。一种方案是将III-V材料(例如GaN和SiC)与CMOS结合使用以获得两种材料的优势。Nadine Collaert给出一个在绝缘的硅衬底(SOI)上生长的具有III-V材料的3D nano-ridge的图片示例,同时指出这里还有很多工作要做。

Imec证明其在绝缘硅衬底(SOI)上生长出III-V材料的3D nano-ridge的能力

至于机器学习对内存的影响则更加明显。 像AI和ML这样的新应用都需要快速地访问内存。 人们迫切需要关注和发展内存计算,随着逻辑和存储的日益紧密,3D封装当然会发挥重要作用。

彼此赋能,量子计算和人工智能可互补

IBM Research总监Dario Gil在会议上进一步提及广义的AI:几乎可以肯定,广义的AI将会在量子计算机上实现。他总结了[敏感词]的好处可能来自bits(数字处理),neurons(AI)和qubits(量子计算)的互补使用。IBM于2016年通过开放了[敏感词]台量子计算机的访问,现在可以访问15台量子计算机,包括其[敏感词]的53量子位模型。

免责声明:本文转载自“新智元”,本文仅代表作者个人观点,不代表萨科微及行业观点,只为转载与分享,支持保护知识产权,转载请注明原出处及作者,如有侵权请联系我们删除。

公司电话:+86-0755-83044319

传真/FAX:+86-0755-83975897

邮箱:1615456225@qq.com

QQ:3518641314 李经理

QQ:332496225 丘经理

地址:深圳市龙华新区民治大道1079号展滔科技大厦C座809室

人类ASIC专家的布局布线结果和一个低功耗ML加速器芯片的布局布线结果对比。谷歌故意遮盖了部分图像。(来源:Google Research / ISSCC)

人类ASIC专家的布局布线结果和一个低功耗ML加速器芯片的布局布线结果对比。谷歌故意遮盖了部分图像。(来源:Google Research / ISSCC)

Google将使用机器学习布局和布线的效果与商用软件进行了比较。 测试电路是几个不同的模块,包括Ariane RISC-V CPU。(来源:Google Research / ISSCC)

Google将使用机器学习布局和布线的效果与商用软件进行了比较。 测试电路是几个不同的模块,包括Ariane RISC-V CPU。(来源:Google Research / ISSCC)

Imec证明其在绝缘硅衬底(SOI)上生长出III-V材料的3D nano-ridge的能力

Imec证明其在绝缘硅衬底(SOI)上生长出III-V材料的3D nano-ridge的能力