As the third generation semiconductor material, SiC is superior to Si-based materials in all aspects. Compared with the traditional power devices based on Si semiconductor materials, the emerging SiC power devices have the advantages of fast switching speed, high blocking voltage and strong high temperature resistance, which can better meet the development requirements of power electronics technology in the future.After three years of in-depth research and development, Shanghai Zhanxin Electronics became the first company in China to master 6-inch SiC MOSFET and SBD technology, as well as SiC MOSFET driver chips. In this paper, the reliability and application of SiC power devices of Zhanxin Electronics are described, so that users can feel at ease before use and worry during use, thus making better products.1. does the SiC MOSFET of Shanghai zhanxin electronics have the data of positive and negative stress limits?The gate voltage specification (+20V/-5V) of SiC MOSFET of Zhanxin Electronics is certified strictly according to JEDEC, which ensures that the working life of products at room temperature is not less than 10 years. For applications beyond the gate voltage specification, there are two main considerations.Firstly, the life model of the gate itself is mainly determined by the TDDB (Time Dependent Dielectric Breakdown) model of SiO2. A large number of data have shown that the quality of the SiO2 dielectric layer grown on SiC is as good as that grown on Si. Therefore, from the perspective of TDDB, the higher voltage that the 20V gate dielectric can withstand and the life model under this voltage are consistent with those of Si MOSFET and IGBT. Zhanxin Electronics is using Zhanxin's own SiC MOSFET to build the life model of SiO2 gate dielectric process and devices.Secondly, the biggest difference and challenge between SiC MOSFET and Si MOS products (MOSFET and IGBT) lies in PBTI (Positive Bias Temperature Instability) and NBTI (Negative Bias Temperature Instability). When positive bias is applied, the device Vth will increase, but when negative bias is applied, the device Vth will decrease. Under the condition of JEDEC certification, the service life of the device can be guaranteed by working within the grid voltage specification; For the application life model beyond the grid voltage specification, Zhanxin Electronics is building equipment and doing detailed planning and research; Generally speaking, as long as the positive gate voltage is not more than 25V and the negative gate voltage is not less than -10V, the relatively small pulse of DutyCycle will not cause irreversible damage to the device performance. The specific quantitative relationship and life model will be given at the end of the first round of research.2. How does Shanghai Zhanxin Electronics solve the problem of establishing negative driving voltage in SiC MOSFET applications? Is this method reliable?Zhanxin Electronics developed the industry's first 35V/4A driver IVCR1401D/IVCR1401DP with 8-pin package and integrated negative voltage drive. After the driver is started, the NEG output is pulled to GND, and the internal current source quickly charges the negative voltage capacitor. After the negative voltage is established, the NEG pin is released, and the internal negative voltage regulator can adjust the negative voltage to -3.5V for normal operation. After that, The gate drive signal NEG switches between (VCC-3.5V) and -3.5, as shown in the following figure, which shows the negative pressure building process of the negative pressure capacitor. It takes about 28us to charge the 1uF capacitor. X7R capacitor, which is more than 100 times Cg capacitor, should be used to reduce the ripple on the negative pressure capacitor, so that the negative pressure can be reliably and stably established and operated and driven. The circuit of the aging test system in our company has been verified by using this chip, and the SiC MOSFET is driven at 1000V/20A/125℃. After 1000 hours of continuous operation, it can still drive stably and reliably.

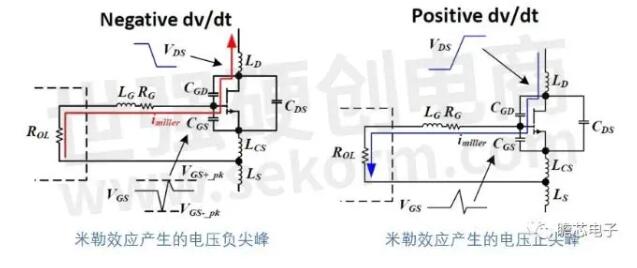

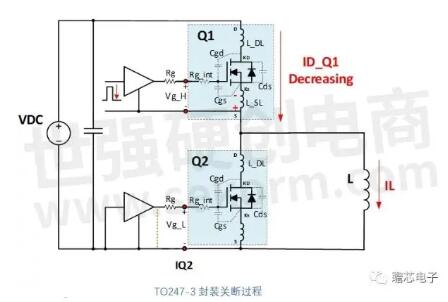

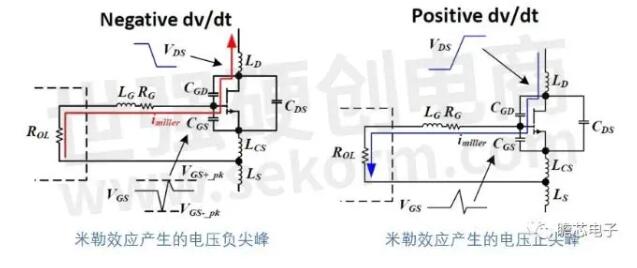

3. How does Shanghai Zhanxin Electronics solve the problem of negative voltage spikes in SiC MOSFET applications? What is the mechanism of negative pressure spike? What's the solution?Compared with traditional Si power devices, SiC MOSFET has faster switching speed. However, this fast transient process will make the switching performance of SiC MOSFET more sensitive to parasitic parameters of the circuit, especially in the driving waveform. The following figure shows the voltage spike caused by Miller effect. In the half-bridge application of SiC MOSFET, when the lower transistor is turned off, a large dv/dt will be generated. Due to the parasitic inductance in the power loop and the driving loop, a large Miller current will be generated, which will generate a voltage drop across the driving resistor RG, resulting in a negative peak on the VGS waveform. Similarly, when the upper tube is turned on, a large dv/dt will also be generated. Due to the parasitic inductance in the loop, a large Miller current will also be generated, which will generate a voltage drop across the driving resistor RG, resulting in a positive peak on the VGS waveform.

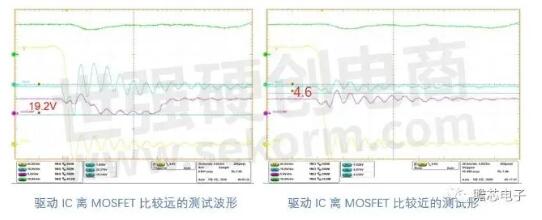

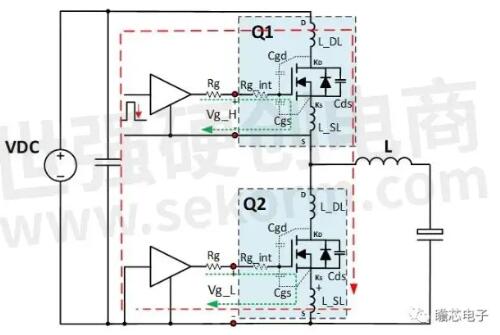

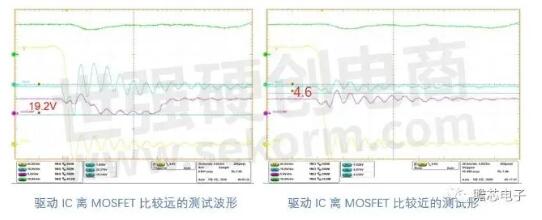

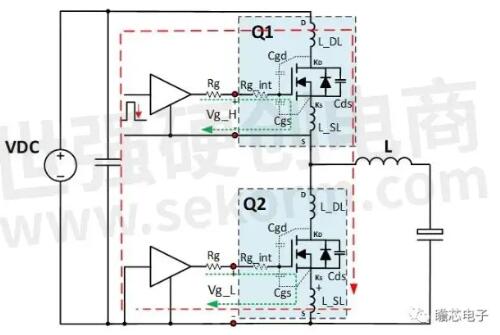

In order to reduce the negative pressure spike of the drive, there are the following suggestions:1) connect a back-to-back MOS (recommended model: QS5K2TR) in parallel with the driving resistor RG to reduce the voltage drop caused by the miller effect on RG, thus reducing the miller peak voltage, as shown in Q1 and Q2 in the following figure;Fig. 3 2) Place the driving chip as close to the gate of SiC MOSFET as possible to reduce the parasitic inductance in the driving circuit as much as possible; 3) Minimize the area of the power loop and the common source inductance in the power loop and the driving loop on the Layout; 4) When conditions permit, use SiC MOSFET packaged in TO247-4, and use Kelvin drive as much as possible to reduce parasitic inductance caused by device pins.4. How does Shanghai Zhanxin Electronics solve the switching oscillation problem in SiC MOSFET applications?The most important thing about the oscillation of SiC MOSFET is to solve the oscillation of driving circuit at first, so as to prevent the oscillation caused by the oscillation of driving signal. To solve the oscillation of the driving circuit, it is necessary to place the driving chip as close as possible to the gate of SiC MOSFET, reduce the parasitic inductance and oscillation as much as possible. The following two figures, the upper figure shows the test waveform of the driver chip far from the SiCMOSFET, and the lower figure shows the test waveform near the driver chip. In the two figures, the sky blue waveform is Vgs waveform, and the yellow waveform is Vds waveform. The miller peak in the left picture is as high as 19.2V, while the miller peak in the right picture is only 4.6V the main reason for this improvement is that the driver IC is close to the SiC MOSFET.

Let's explain some points of attention in the Layout of SiC MOSFET. A good Layout helps to reduce the oscillation. At first, the driver IC should be as close to the SiC MOSFET as possible to ensure that the smaller the area of the driver circuit, the better. Secondly, the high frequency oscillation is caused by the oscillation between stray inductance and stray capacitance (mainly Coss) of PCB and MOSFET. In the following figure, the red dotted line is the area of the power circuit, and the green dotted line is the area of the driving circuit. The smaller these areas are, the smaller the oscillation of SiC MOSFET will be.

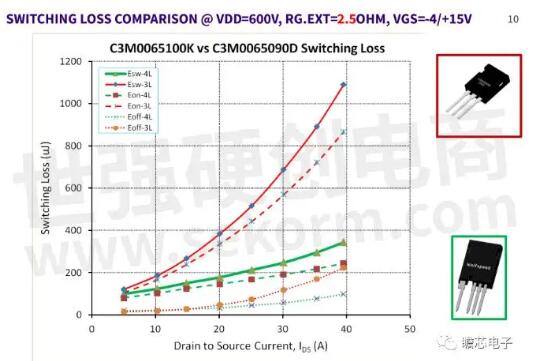

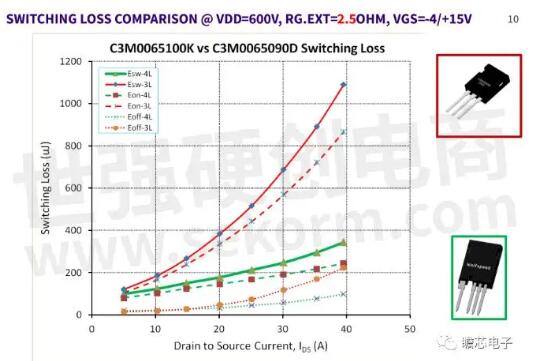

5. Similarities and differences between SiC MOSFET drive and Si IGBT drive? Can SiC MOSFET be driven by IGBT plug-in driver board?Can't be used. Because the driving board is adopted, the parasitic inductance of the driving circuit is relatively large, which requires a larger driving resistance to damp, which leads to slower switching speed and higher loss. If it is not damped by a larger driving resistor, the Vgs waveform will lead to a larger oscillation, which will lead to Vds oscillation, thus increasing the switching loss. In addition, the larger parasitic inductance itself increases the impedance of the driving circuit, and the Miller resistance of the driving circuit weakens, resulting in slower switching speed and higher loss.6. What should be paid attention to in parallel connection of SiC MOSFET?To ensure that the driving circuit and the main power circuit of each SiC MOSFET are as symmetrical as possible, it is required that the distance from the output of the driving chip to the gate of each SiC MOSFET is all the same, and each SiC MOSFET needs a separate Rg to increase the consistency. If parallel MOSFETs share a driving resistor, the MOSFET with the lowest threshold voltage will be turned on first, and the Vgs of other MOSFETs will be clamped at this threshold voltage, thus only the MOSFET with the lowest threshold voltage will be turned on, and all other tubes will not be turned on. The same is true for the turn-off process. The MOSFET with the highest threshold voltage is turned off first, and the voltage is clamped at the threshold voltage at the same time until the transistor is turned off. It can be seen that using one driving resistor to drive all the MOSFET will cause relatively large dynamic uneven current at the switching moment. Therefore, it is necessary to configure a separate Rg for each MOSFET, so as to decouple the Vgs of each MOSFET and enhance the dynamic current sharing. The static current sharing characteristic of MOSFET is mainly realized by the parameter consistency of MOSFET itself, so it is necessary to carefully select MOSFETs with the same parameters for direct parallel connection.Figure 68. How much is the parasitic inductance of SiC MOSFET TO 247-4 improved compared with TO247-3? Are there any specific parameters?According to the data published by CREE, the switching loss of TO247-4 package is only 30%(600V/40A) of that of TO247-3 package. Therefore, the advantages of TO247-4 package are very obvious.

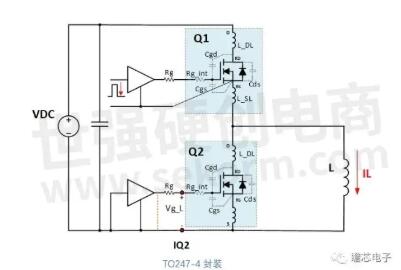

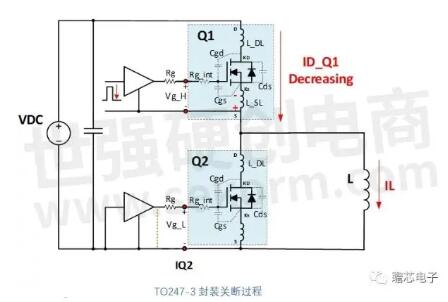

The internal common Source inductor inside the TO247-3 package will slow down the turn-on and turn-off speed of the MOSFET, thus increasing the switching loss. However, because the TO247-4 has a separate Source lead for driving, it bypasses the internal common Source inductor, thus avoiding the influence of the internal common Source inductor on the switching process, thus achieving the purpose of reducing the switching loss. First, look at the opening process. In a typical double-pulse experiment, it is realized by switching the upper tube. We mainly focus on the upper tube Vgs circuit. When the upper transistor is turned on, the Id of Q1 is increased, so the voltage induced by L_SL is positive at the top and negative at the bottom, and its voltage has the same polarity as the external driving voltage (positive voltage), resulting in the decrease of Vgs voltage on the internal MOSFET-Die, thus slowing down the MOSFET turning-on process.Figure 8Let's look at the turn-off process of the upper tube. Q1 turns off, which leads to the decrease of Id. The voltage induced by L_SL is negative at the top and positive at the bottom. This voltage is opposite to the external driving voltage (negative or zero voltage), which will reduce the voltage of Vgs on the actual internal MOSFET-Die during the turn-off process. If the voltage on L_SL is large enough, it can even cause the voltage on the internal MOSFET-Die to change from negative voltage to positive voltage, resulting in false turn-on! Therefore, L_SL will slow down the turn-off process, thus increasing the turn-off loss.

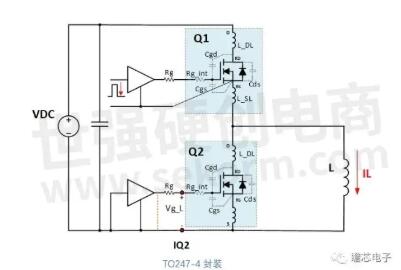

The figure below uses the TO247-4 package, because there is a single Kelvin-Source lead, so that the induced voltage on L_SL cannot affect the driving circuit, thus increasing the switching speed and reducing the switching loss.

Disclaimer: This article is reproduced from "INSEMI". This article only represents the author's personal views, and does not represent the views of Sacco Micro and the industry. It is only for reprinting and sharing to support the protection of intellectual property rights. Please indicate the original source and author when reprinting. If there is any infringement, please contact us to delete it.

Company Tel: +86-0755-83044319

Fax/fax:+86-0755-83975897

Email: 1615456225@qq.com

QQ: 3518641314 Manager Li

QQ: 332496225 Manager Qiu

Address: Room 809, Block C, Zhantao Technology Building, No.1079 Minzhi Avenue, Longhua New District, Shenzhen