Service hotline

+86 0755-83044319

release time:2023-09-09Author source:SlkorBrowse:17093

3. Summary of Basic Characteristics

Due to structural differences, GaN power devices have different characteristics compared to silicon-based devices.

(1) Standard Voltage: 650V

The typical voltage for GaN power devices is 650V. In many power supply applications, the input is connected to the 220V AC mains. After rectification, the voltage on the bus capacitor reaches approximately 400V DC. In addition, there are voltage spikes and reflection from secondary side in certain topology applications. Therefore, 650V has become a standard voltage requirement.

(2) No Avalanche Breakdown

GaN power devices do not experience avalanche breakdown. Once breakdown occurs, it is permanent, similar to dielectric breakdown in capacitors. For a 650V device, if it were a silicon MOSFET, the actual breakdown voltage is typically around 750V (with a design margin of 10%). However, GaN devices require a higher breakdown voltage design margin. A 650V device needs a breakdown voltage of at least 900V (with a design margin >10%).

(3) No p-type GaN Transistors

In silicon-based technology, there are NMOS (electron carrier) and PMOS (hole carrier), but currently, there are no p-type GaN HEMTs. Therefore, the design of analog/digital ICs is different from silicon. The main reasons for the lack of p-type GaN transistors are: firstly, ion implantation and low-temperature annealing of magnesium ions are difficult to achieve on GaN; secondly, the hole mobility of GaN is only 30cm²/Vs, much lower than the electron mobility of 2000cm²/Vs.

(4) Gate Voltage: 7V

Due to the GaN process, the maximum gate voltage for GaN power devices is limited to 7V, which is incompatible with existing silicon driver ICs.

Device Process Technology

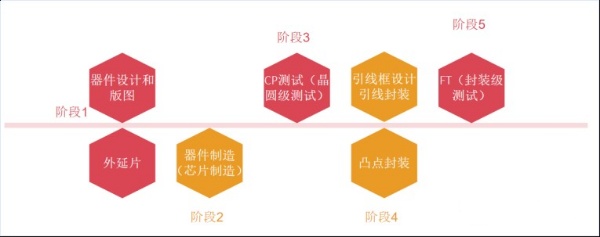

GaN power devices, like silicon-based chips, undergo similar manufacturing processes, which mainly include design, epitaxial wafer growth, chip fabrication, and packaging testing.

Figure 4:Typical Manufacturing Steps for GaN Power Devices

1. Design Phase

GaN devices are typically simulated and modeled during the design phase using TCAD (Technology Computer-Aided Design) techniques. This involves simulating and analyzing the device's structure and parameters.

2. Epitaxial Wafer Manufacturing Process

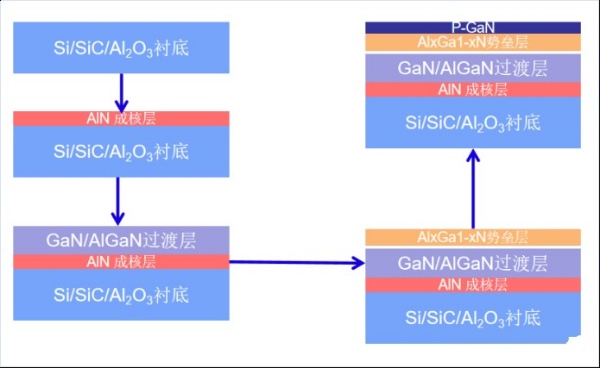

GaN epitaxial wafers can be grown on silicon substrates, silicon carbide substrates, or sapphire substrates. For cost and mass production considerations, the deposition of each layer in the epitaxial wafer is typically performed using the MOCVD (Metal Organic Chemical Vapor Deposition) technique.

Figure 5: Manufacturing Process of GaN Epitaxial Wafer

3. Device Manufacturing Process

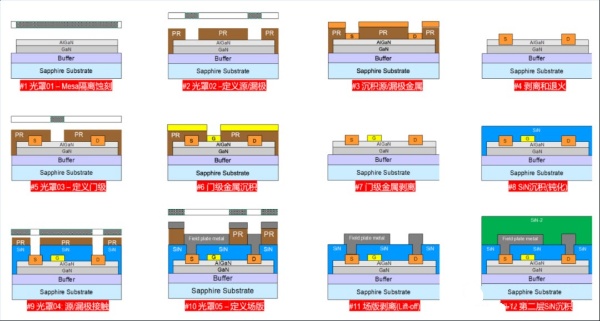

The simplified process flow for the fabrication of depletion-mode GaN HEMT (High Electron Mobility Transistor) devices on sapphire substrates is shown in the figure below. The process flow for GaN HEMT devices on silicon substrates is similar.

The first step involves the use of the first mask for platform-type isolation etching. The second step utilizes the second mask to define the source and drain regions. The third step involves the deposition of metal for the source and drain. The fourth step includes glass deposition and annealing to form the source and drain metal regions. The fifth step uses the third mask to define the gate region. The sixth step involves the deposition of metal for the gate. The seventh step entails metal lift-off to create the gate metal. The eighth step involves depositing silicon nitride for passivation and protection. The ninth step utilizes the fourth mask to define the contacts for the source and drain regions. The tenth step employs the fifth mask to define the field plate. The eleventh step involves metal lift-off to form the field plate, and the twelfth step entails depositing a second layer of silicon nitride for passivation.

Note: The specific steps and mask numbers mentioned may vary depending on the device design and the manufacturing process used.

Figure 6: Process Flow for D-mode GaN HEMT Fabrication on Sapphire Substrate

4. CP Testing

CP testing mainly involves testing various parameters in both room temperature and high-temperature environments to identify defective chip dies on the wafer. These defective chips are then marked with a dye and excluded from further packaging processes.

Figure 7: CP Testing (Red Indicates the Locations of Defective Chips)

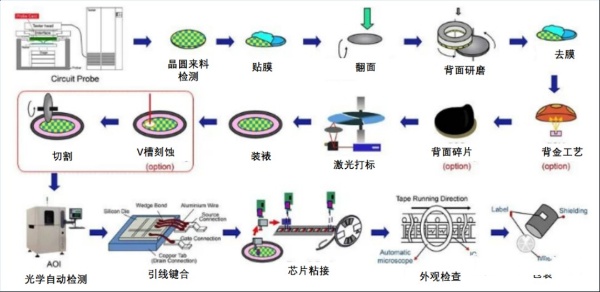

5. Packaging

Figure 8: Simplified Packaging Steps

To be continued...

Site Map | 萨科微 | 金航标 | Slkor | Kinghelm

RU | FR | DE | IT | ES | PT | JA | KO | AR | TR | TH | MS | VI | MG | FA | ZH-TW | HR | BG | SD| GD | SN | SM | PS | LB | KY | KU | HAW | CO | AM | UZ | TG | SU | ST | ML | KK | NY | ZU | YO | TE | TA | SO| PA| NE | MN | MI | LA | LO | KM | KN

| JW | IG | HMN | HA | EO | CEB | BS | BN | UR | HT | KA | EU | AZ | HY | YI |MK | IS | BE | CY | GA | SW | SV | AF | FA | TR | TH | MT | HU | GL | ET | NL | DA | CS | FI | EL | HI | NO | PL | RO | CA | TL | IW | LV | ID | LT | SR | SQ | SL | UK

Copyright ©2015-2025 Shenzhen Slkor Micro Semicon Co., Ltd