Service hotline

+86 0755-83044319

release time:2023-09-12Author source:SlkorBrowse:13855

The etching steps for nanosheet FETs

The most critical etching steps in the nanoribbon fabrication process include pseudo-gate etching, anisotropic pillar etching, isotropic spacer etching, and channel release step. The contour etching of alternating layers of silicon and SiGe is anisotropic and employs fluorine-based chemistry. The etching of internal spacers (indentations) and the channel release step are optimized to achieve minimal silicon loss in SiGe.

The channel release step is crucial. "The release of nanoribbons requires high selectivity," Bézard said. "Most nanoribbons consist of silicon, then SiGe and silicon again. You have alternating layers, and you need to remove one layer without modifying the other." Some publications discuss performing multi-step SiGe etching to reduce the stress induced on the structure by a single etching step.

The next step in the process is forming self-aligned contacts. "Here, what we try to do is essentially etching oxide instead of contacting or recessing nitride. For example, the current specification is a 3-micrometer recess, but people ask for zero loss," Bézard said. "In this case, we don't even use the word selectivity. We just talk about stopping—and zero stop."

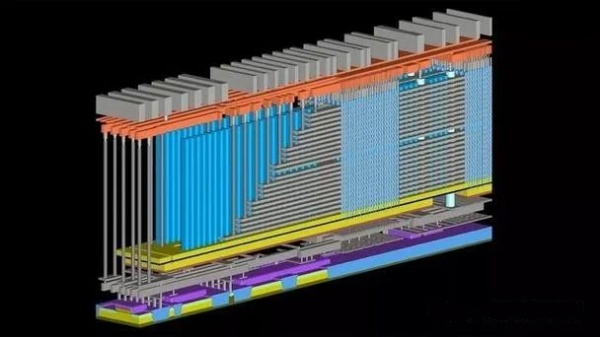

3D NAND

For 3D NAND flash, as the number of layers continues to increase, there is a need to adopt multiple stacked layers to form the vertical string of stacked devices. Robert Clark states, "Furthermore, with the increase in layers, there is a strong drive to scale the wordline pitch or the vertical/Z spacing of the layers in order to further increase bit density." This comes from senior members of TEL's technical staff and technology directors. From a process perspective, etching and deposition processes need constant improvement to accommodate the increasingly smaller critical dimensions and higher aspect ratios required for scaling.

Clark describes the future changes, saying, "Looking at advanced nodes for multi-layer charge trap devices, engineering the gate-stack will be needed to achieve shorter gate lengths, more energy levels per cell, and improved programming efficiency, potentially achieved through the adoption of high-k materials. There may also be a need for higher conductivity channels to replace poly-Si channels."

One of the most critical etch steps in 3D NAND involves deep etching of approximately 100nm holes through a stack of over 200 layers of oxide and nitride, with depths reaching 10µm. Bézard from imec states that this etch step is particularly expensive.

"We have a physical phenomenon called the differential charging effect," he says. "In plasmas, we have electrons, ions, and neutral species to simplify things. Electrons move in all directions, but ions accelerate vertically to the surface. So, at the bottom of the hole, you have positive charges, and at the top, negative charges, creating an electric field that tries to repel incoming ions."

As a result, high power levels are needed to fully etch the trenches. He adds, "We are working on maintaining power levels of 30-50 kilowatts without generating arcing, so the chuck must be very well polished and manufactured."

Deep etching also gives rise to stress that needs to be minimized, especially since subsequent steps in multi-layer NAND manufacturing involve thinning the chips, precise alignment, and hybrid bonding with the next layer.

Other processes

Not all chip manufacturers produce cutting-edge chips that require EUV lithography. Many fabs are expanding their 193nm lithography and etching processes.

Brian Wilbur, the Director of Semiconductor Product Diversification at Bruel Science Corporation, states, "We have recently introduced a high-temperature SOC material that extends its patterning capability and can withstand higher temperatures, whether used as an underlayer for CVD layers or as a mask."

The BEOL (Back-End-of-Line) used for the tightest metal lines is expected to undergo a dramatic shift from dual-damascene integration schemes to subtractive deposition and etching for interconnects other than copper. In this regard, rhenium and molybdenum have seen the most significant developments. They have different advantages. Molybdenum is more prone to oxidation during etching, making it more compatible with dual-damascene schemes and also cheaper in price. Rhenium is a precious metal, so it doesn't have the same corrosion issues, but it comes with much higher costs.

Device structures are also becoming less tolerant of edge placement errors. Clark from TEL states that new approaches will be needed to achieve self-alignment between layers, as well as between vias and interconnects. "The first implementations may be buried word lines for DRAM and small-spacing metal layers in MOL for logic, where higher thermal stability and lower resistivity or non-linear metals are required."

Next-generation development

Looking ahead in the long term, ideally, the industry will transition to back-end processes with lower thermal budgets (closer to 300°C instead of 400°C) to enable the integration of devices into the back-end interconnect layers.

Clark from TEL stated, "The industry does need to start building devices in more layers. It means we need to build memory and logic devices within the back-end of line (BEOL) thermal budget."

Clark also mentioned that devices manufactured using semiconductor oxide seem promising so far, whether it's integrating memory devices into the logic BEOL flow or building CMOS arrays on storage arrays in DRAM.

Another significant shift involves the integration of 2D materials, which research institutions and leading chip manufacturers have begun testing. Consideration is given to etching materials such as tungsten disulfide or molybdenum disulfide. However, developing wafer manufacturing processes that integrate these thin films, consisting of just a single layer of material, poses significant challenges.

Sustainability

Chip manufacturers and material suppliers are seeking alternative chemicals to reduce carbon emissions. In etching processes, the main culprit is fluorinated gases with high global warming potential (GWP).

Bézard from imec stated, "The problem with PFAS is that its molecules are highly stable. Light or chemical reactions in the atmosphere are not sufficient to break it down."

He mentioned that many alternative gas mixtures with higher oxygen content are easier to dissociate and have lower global warming potential values. However, any candidate must demonstrate equal or better performance to be considered.

But sustainability is not just a specific challenge for etching or deposition. From lithography to packaging, it is a comprehensive industry challenge where the impact of new materials will affect the entire device fabrication.

Site Map | 萨科微 | 金航标 | Slkor | Kinghelm

RU | FR | DE | IT | ES | PT | JA | KO | AR | TR | TH | MS | VI | MG | FA | ZH-TW | HR | BG | SD| GD | SN | SM | PS | LB | KY | KU | HAW | CO | AM | UZ | TG | SU | ST | ML | KK | NY | ZU | YO | TE | TA | SO| PA| NE | MN | MI | LA | LO | KM | KN

| JW | IG | HMN | HA | EO | CEB | BS | BN | UR | HT | KA | EU | AZ | HY | YI |MK | IS | BE | CY | GA | SW | SV | AF | FA | TR | TH | MT | HU | GL | ET | NL | DA | CS | FI | EL | HI | NO | PL | RO | CA | TL | IW | LV | ID | LT | SR | SQ | SL | UK

Copyright ©2015-2025 Shenzhen Slkor Micro Semicon Co., Ltd